## **TMC2301**

# Image Resampling Sequencer 15, 18, 20 MHz

#### **Features**

- Rotation, warping, panning, zooming, and compression of images in real time

- 20 MHz clock rate

- 4096 x 4096 image field addressing capability

- User-selectable nearest-neighbor, bilinear interpolation, and cubic convolution resampling algorithms

- Static convolutional filtering of up to 16 x 16 pixel windows

- Single-pass or two-pass convolution operations

- Low power consumption CMOS process

- Single 5V power supply

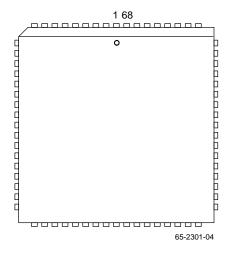

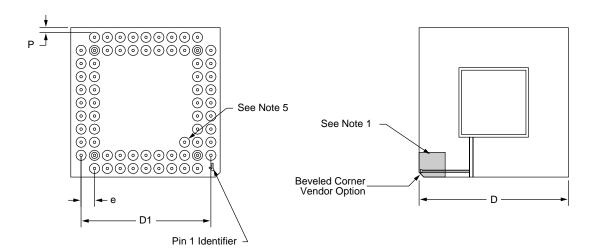

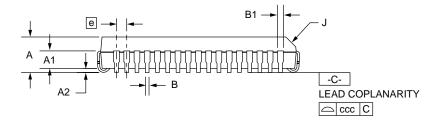

- Available in a 68-pin grid array and low-cost plastic leaded chip carrier (J-bend)

## **Applications**

- Video special-effects generators

- Image recognition systems, robotics

- Artificial intelligence

- High-precision image registration (LANDSAT processing)

- · High-speed data encoding/decoding

- General purpose image processing

- Image data compression

### **Description**

The TMC2301 is a VLSI circuit which supports image resampling, rotation, rescaling and filtering by generating input bit plane, interpolation coefficient lookup table, and output bit plane memory addresses along with external multiplier-accumulator control signals. The TMC2301 can process data fields of up to 4096 x 4096 multibit words at a clock rate of up to 20 MHz. An Image Resampling

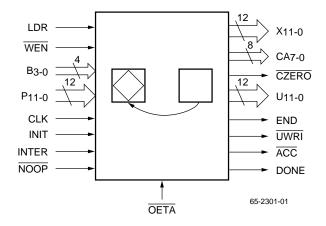

## **Logic Symbol**

Sequencer (IRS) based system can nearest-neighbor resample a 512 x 512 image in 15 milliseconds, translating, zooming, rotating, or warping it, depending on the transform parameter set loaded. A complete bilinear interpolation of the same image can be completed in 60 milliseconds. Image resampling speed is independent of the angle of rotation, degree of warp, or amount of zoom specified.

A high performance, TMC2301-based system can execute bilinear and cubic convolution algorithms that rotate images accurately and in real time. Keystone or other perspective correction, image plane distortion, and numerous other second order polynomial transformations can be programmed and executed under direct user control. Direct access to the interpolation coefficient lookup table allows dynamic modification of the algorithm.

Following an initialization with the transform parameters and control bits defining the operation to be executed, the IRS assumes control of the input and output data fields and executes unattended. All inputs except INTER and all outputs are registered on the rising edge of clock. All outputs are three-state controlled except  $\overline{ACC}$ ,  $\overline{CZERO}$ , END, and DONE.

Fabricated in a 1 micron CMOS process, the TMC2301 operates at clock rates of up to 20 MHz over the full commercial (0 to 70°C) temperature and supply voltage ranges, and at 15 MHz over the extended (-55 to +125°C) temperature and supply voltage ranges. All signals are TTL compatible.

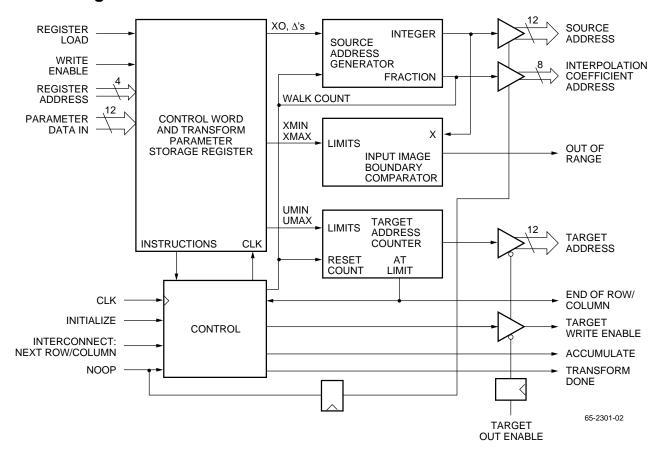

### **Block Diagram**

## **Functional Description**

#### **General Information**

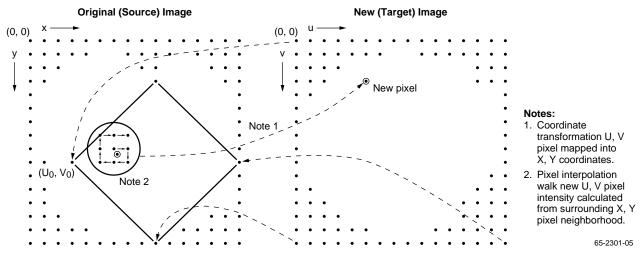

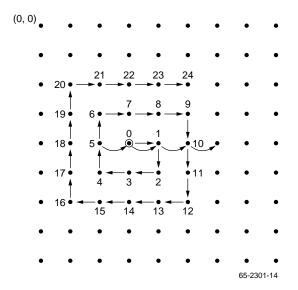

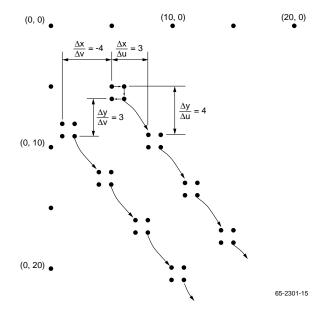

The IRS is a versatile self-sequencing address generator designed primarily to filter a two-dimensional image or to remap and resample it from one set of Cartesian coordinates (x, y) into a new transformed set (u, v). Most applications use two identical devices in tandem, one generating the row coordinates (X and U), the other generating the column coordinates (Y and V). The algorithm performed by the TMC2301 consists of two steps: a coordinate system transformation, followed by pixel interpolation. Interpolation is necessary when the transformed pixel positions (U, V) do not coincide with the original pixel positions (X, Y). The new pixel intensity values are obtained by interpolating the original pixels in the neighborhood of the transformed pixel positions. See Figure 1.

The IRS executes a general second order coordinate transformation of the form:

$$X(u, v) = Au^{2} + Bu + Cuv + Dv^{2} + Ev + F$$

$Y(u, v) = Gu^{2} + Hu + Kuv + Lv^{2} + Mv + N$

where A through N are user-defined parameters. It steps sequentially through the pixels of a user-defined rectangle in

the new set of coordinates, computing the "old" address (X,Y) corresponding to each "new" location (U,V).

The TMC2301 uses the external multiplier-accumulator, connected to the system clock, to calculate the interpolated pixel value by summing the products of the original pixel values stored in the source buffer RAM and the appropriate weights from the polynomial transform lookup table. The new interpolated image value is then stored in the corresponding (U, V) memory location. Finally, the new image address is incremented by one pixel in the "U" direction or reset to the start of the next line (with "V" incremented) proceeding line-by-line through the entire destination image.

The TMC2301 can support any nearest neighbor, bilinear, or cubic resampling, according to the user's requirements. The bilinear and cubic kernels require a coefficient lookup table and multiplier-accumulator. Both one-pass and two-pass algorithms are supported. Sophisticated "walkaround" algorithms implementing static filters are also easily realized utilizing convolutional kernels of up to 16 x 16 pixels. For each output point in a typical static single-pass filter, the IRS will generate a series of addresses, "walking" around that point in two dimensions. At the end of each walk, it will advance one pixel along the output scan line, then begin the walk for the next pixel.

Figure 1. Image Resampling Geometry Showing Image Rotation and Expansion

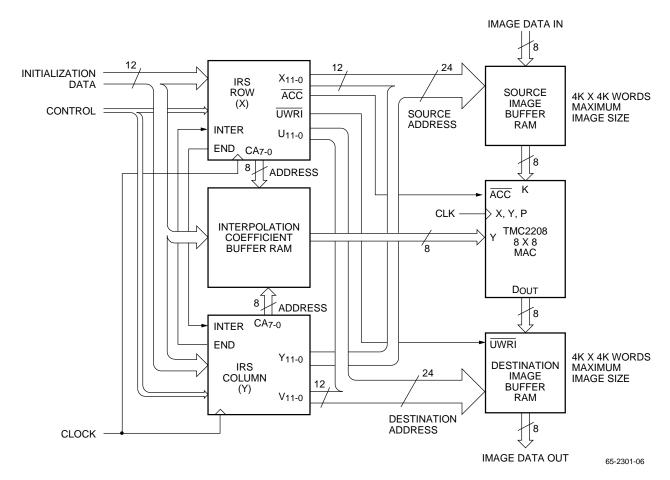

A basic TMC2301-based system is shown in Figure 2. In this typical system, two Image Resampling Sequencers process the image. The only other external parts needed are a

multiplier-accumulator, external interpolation coefficient lookup table RAM, and the user-specified Source and Destination Image Memory.

Figure 2. Basic 2-D Image Convolver Using TMC2301 Image Resampling Sequencer

Utilizing Typical 8-Bit Data Path

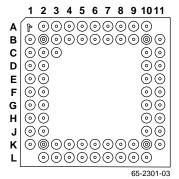

## **Pin Assignments**

## 68 Pin Grid Array

| Pin | Name           | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| B2  | INIT           | K2  | U <sub>10</sub> | K10 | X <sub>1</sub>  | B10 | P <sub>6</sub>  |

| B1  | OETA           | L2  | U <sub>11</sub> | K11 | X <sub>2</sub>  | A10 | P <sub>5</sub>  |

| C2  | INTER          | K3  | UWRI            | J10 | Х3              | B9  | P <sub>4</sub>  |

| C1  | END            | L3  | ACC             | J11 | X4              | A9  | P3              |

| D2  | DONE           | K4  | CZERO           | H10 | X <sub>5</sub>  | B8  | P <sub>2</sub>  |

| D1  | U <sub>0</sub> | L4  | CA <sub>0</sub> | H11 | X <sub>6</sub>  | A8  | P <sub>1</sub>  |

| E2  | U <sub>1</sub> | K5  | CA <sub>1</sub> | G10 | X <sub>7</sub>  | В7  | P <sub>0</sub>  |

| E1  | U <sub>2</sub> | L5  | $V_{DD}$        | G11 | X <sub>8</sub>  | A7  | CLK             |

| F2  | GND            | K6  | GND             | F10 | GND             | B6  | GND             |

| F1  | U <sub>3</sub> | L6  | CA <sub>2</sub> | F11 | X9              | A6  | V <sub>DD</sub> |

| G2  | U <sub>4</sub> | K7  | CA <sub>3</sub> | E10 | X <sub>10</sub> | B5  | NOOP            |

| G1  | U <sub>5</sub> | L7  | CA <sub>4</sub> | E11 | X <sub>11</sub> | A5  | LDR             |

| H2  | U <sub>6</sub> | K8  | CA <sub>5</sub> | D10 | P <sub>11</sub> | B4  | В0              |

| H1  | U <sub>7</sub> | L8  | CA <sub>6</sub> | D11 | P <sub>10</sub> | A4  | B <sub>1</sub>  |

| J2  | U <sub>8</sub> | K9  | CA <sub>7</sub> | C10 | P <sub>9</sub>  | В3  | B <sub>2</sub>  |

| J1  | U <sub>9</sub> | L9  | X <sub>0</sub>  | C11 | P8              | А3  | B <sub>3</sub>  |

| K1  | GND            | L10 | GND             | B11 | P <sub>7</sub>  | A2  | WEN             |

#### 68 Pin PLCC

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | GND             | 18  | GND             | 35  | GND             | 52  | GND             |

| 2   | CA <sub>2</sub> | 19  | X9              | 36  | V <sub>DD</sub> | 53  | U <sub>3</sub>  |

| 3   | CA <sub>3</sub> | 20  | X <sub>10</sub> | 37  | NOOP            | 54  | U <sub>4</sub>  |

| 4   | CA <sub>4</sub> | 21  | X11             | 38  | LDR             | 55  | U <sub>5</sub>  |

| 5   | CA <sub>5</sub> | 22  | P11             | 39  | B <sub>0</sub>  | 56  | U <sub>6</sub>  |

| 6   | CA <sub>6</sub> | 23  | P <sub>10</sub> | 40  | B <sub>1</sub>  | 57  | U <sub>7</sub>  |

| 7   | CA <sub>7</sub> | 24  | P9              | 41  | B <sub>2</sub>  | 58  | U <sub>8</sub>  |

| 8   | X <sub>0</sub>  | 25  | P <sub>8</sub>  | 42  | В3              | 59  | U <sub>9</sub>  |

| 9   | GND             | 26  | P <sub>7</sub>  | 43  | WEN             | 60  | GND             |

| 10  | X <sub>1</sub>  | 27  | P <sub>6</sub>  | 44  | INIT            | 61  | U <sub>10</sub> |

| 11  | X <sub>2</sub>  | 28  | P <sub>5</sub>  | 45  | OETA            | 62  | U <sub>11</sub> |

| 12  | Х3              | 29  | P4              | 46  | INTER           | 63  | UWRI            |

| 13  | X <sub>4</sub>  | 30  | P <sub>3</sub>  | 47  | END             | 64  | ACC             |

| 14  | X5              | 31  | P <sub>2</sub>  | 48  | DONE            | 65  | CZERO           |

| 15  | X <sub>6</sub>  | 32  | P <sub>1</sub>  | 49  | U <sub>0</sub>  | 66  | CA <sub>0</sub> |

| 16  | X <sub>7</sub>  | 33  | P <sub>0</sub>  | 50  | U <sub>1</sub>  | 67  | CA <sub>1</sub> |

| 17  | X8              | 34  | CLK             | 51  | U <sub>2</sub>  | 68  | V <sub>DD</sub> |

## **Pin Descriptions**

|                   | Pin Number                                                            |                         |                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name          | PGA                                                                   | PLCC                    | Pin Function Description                                                                                                                                                                                                                                                                                                                                     |  |

| Power             |                                                                       |                         |                                                                                                                                                                                                                                                                                                                                                              |  |

| GND               | F2, F10, K1,<br>K6, L10, B6                                           | 1, 9, 18, 35,<br>52, 60 | <b>Supply Voltage.</b> The TMC2301 operates from a single +5V supply. All pins must be connected.                                                                                                                                                                                                                                                            |  |

| V <sub>DD</sub>   | L5, A6                                                                | 36, 68                  | <b>Ground.</b> The TMC2301 operates from a single +5V supply. All pins must be connected.                                                                                                                                                                                                                                                                    |  |

| Clock             | •                                                                     |                         |                                                                                                                                                                                                                                                                                                                                                              |  |

| CLK               | A7                                                                    | 34                      | <b>System Clock.</b> The TMC2301 has a angle clock input. The rising edge of CLK strobes all enabled registers. All timing specifications are referenced to the rising edge of CLK.                                                                                                                                                                          |  |

| Inputs            | •                                                                     |                         |                                                                                                                                                                                                                                                                                                                                                              |  |

| B <sub>3-0</sub>  | A3, B3, A4, B4                                                        | 42-39                   | Parameter Register Address. The write addresses for the individual coordinate transform parameters are presented at the registered 4-bit B input port. B <sub>3</sub> is the Most Significant Bit.                                                                                                                                                           |  |

| P11-0             | D10, D11,<br>C10, C11,<br>B11, B10, A10,<br>B9, A9, B8,<br>A8, B7     | 22-33                   | Parameter Register Data. The coordinate transformation parameters are loaded through the registered 12-bit P input port. P11 is the Most Significant Bit.                                                                                                                                                                                                    |  |

| Outputs           | <u>'</u>                                                              | ļ                       |                                                                                                                                                                                                                                                                                                                                                              |  |

| CA <sub>7-0</sub> | K9, L8, K8, L7,<br>K7, L6, K5, L4                                     | 7-2, 67, 66             | Coefficient Address. The current interpolation kernel coefficient lookup table address is indicated by the registered 8-bit CA7-0 output bus. This output is forced to the high impedance state when NOOP is LOW. CA7 is the Most Significant Bit.                                                                                                           |  |

| U <sub>11-0</sub> | L2, K2, J1, J2,<br>H1, H2, G1,<br>G2, F1, E1,<br>E2, D1               | 62, 61, 59-53,<br>51-49 | <b>Target Address.</b> The U (or V) target address of the image being generated is indicated by the registered 12-bit U <sub>11-0</sub> output bus. This output is forced to the high impedance state when OETA is HIGH. U <sub>11</sub> is the Most Significant Bit.                                                                                        |  |

| X11-0             | E11, E10, F11,<br>G11, G10,<br>H11, H10, J11,<br>J10, K11, K10,<br>L9 | 21-19, 17-10,<br>8      | <b>Source Address.</b> The current X (or Y) source pixel address of the image being resampled is indicated by the registered 12-bit $X_{11-0}$ output bus. This output is forced to the high impedance state when $\overline{NOOP}$ is LOW. $X_{11}$ is the Most Significant Bit.                                                                            |  |

| Controls          | '                                                                     | I.                      |                                                                                                                                                                                                                                                                                                                                                              |  |

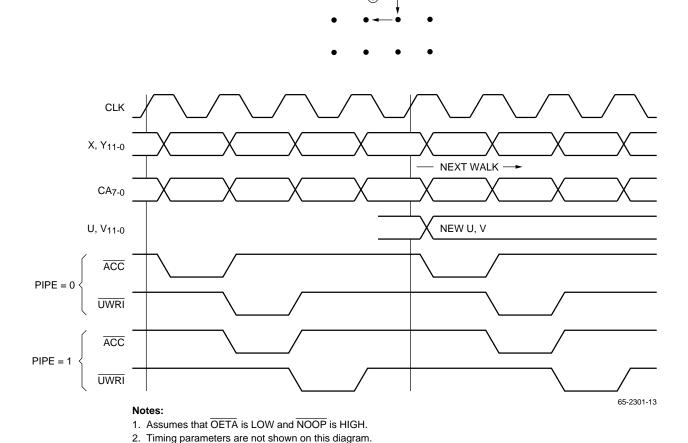

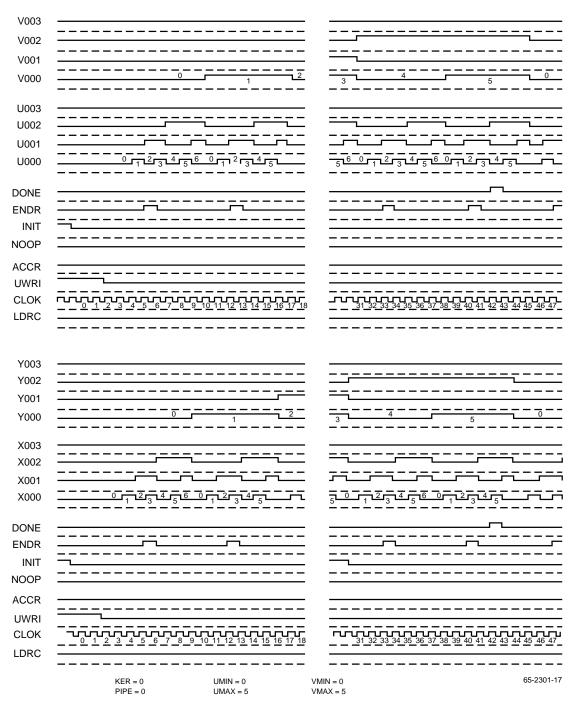

| ACC               | L3                                                                    | 64                      | Accumulate. The accumulation register of the external multiplier-accumulator is initialized by the registered $\overline{ACC}$ output. $\overline{ACC}$ goes LOW for one cycle at the start of each interpolation "walk," effectively clearing the storage register by loading in only the new first product. See Figure 9.                                  |  |

| INIT              | B2                                                                    | 44                      | Initialize. The control logic is cleared and initialized for the start of a new image transformation when the registered INIT input is HIGH for a minimum of two clock cycles. Normal operation begins after INIT goes LOW.                                                                                                                                  |  |

| INTER             | C2                                                                    | 46                      | Interconnect. In the common two-device system configuration, the Interconnect inputs are connected to the END flag outputs. The END flag from the row (X) sequencer thus indicates an "end of line" to the column (Y) device, while the column sequencer in turn sends a "bottom of frame" signal to the row device, forcing a reset of the address counter. |  |

## Pin Descriptions (continued)

|          | Pin Number |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | PGA        | PLCC | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

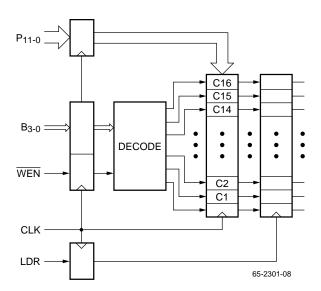

| LDR      | A5         | 38   | Load Parameter Data Registers. The data held in all transformation parameter preload registers are latched into the working registers when the registered input LDR is HIGH. When LDR is LOW, the working parameters remain unchanged. See Figure 4.                                                                                                                                                                                                                                                                                                                                                                  |  |

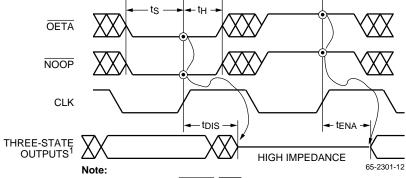

| NOOP     | B5         | 37   | <b>No Operation.</b> The Clock is overidden when the registered input NOOP is LOW, holding each address generator in their current state. Also, the output buffers for the address busses X <sub>11-0</sub> and CA <sub>7-0</sub> are forced to the high impedance state. This allows the user access to all external memory. When NOOP goes HIGH, normal operation resumes on the next clock cycle.                                                                                                                                                                                                                  |  |

| OETA     | B1         | 45   | Target Memory Output Enable. The target memory outputs UWRI and address bus U <sub>11-0</sub> are in the high-impedance state when the registered Output Enable input is HIGH. When OETA is LOW, they are enabled on the next clock cycle.                                                                                                                                                                                                                                                                                                                                                                            |  |

| ŪWRĪ     | K3         | 63   | Target Memory Write Enable. After the end of each interpolation "walk," the Target Memory (U or V) Write Enable goes LOW for one clock cycle. See Figure 9. This registered output is forced to the high impedance state when OETA is HIGH.                                                                                                                                                                                                                                                                                                                                                                           |  |

| WEN      | A2         | 43   | <b>Parameter Write Enable.</b> The registered Write Enable input allows the transformation parameters to be written into the preload register indicated by the address at the B input port when LOW. See Figure 4.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Flags    |            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

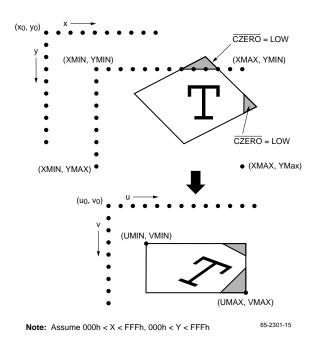

| CZERO    | K4         | 65   | <b>Coefficient Zero.</b> The registered $\overline{\text{CZERO}}$ flag of a horizontal dimension TMC2301 goes HIGH if X < 0, XMIN $\leq$ X $\leq$ XMAX, or X $\geq$ 4096 (1000 hex). It goes LOW if $0 \leq$ X $\leq$ XMIN or XMAX < X < 4096. The logical AND of the $\overline{\text{CZERO}}$ flags of a two-dimensional pair of TMC2301s will go LOW when the source address falls outside a rectangle with vertices (XMIN, YMIN), (XMAX, YMIN), (XMIN, YMAX), and (XMAX, YMAX), denoting an invalid address. The external data path can be wired to substitute a selected background value whenever this AND = 0. |  |

| DONE     | D2         | 48   | <b>End of Transform.</b> In the standard two-device system, a row sequencer DONE flag HIGH after the last walk at the end of the last row of an image (during UWRI LOW) indicates the end of the transform. This registered output is usually ignored on the column device. See the Transformation Control Parameters, AUTOINIT.                                                                                                                                                                                                                                                                                      |  |

| END      | C1         | 47   | End of Row/Page. The registered END flag goes HIGH during the last pixel of the last walk in a row in the case of the row chip, and the last pixel of the last walk in a column in the column chip, in the two-device architecture. This output is used as the end-of-line and end-of-frame indicator in conjunction with the INTER inputs of both TMC2301s.                                                                                                                                                                                                                                                          |  |

## **Transformation Control Parameters**

The TMC2301 is a self-sequencing device which requires no cycle-to-cycle intervention from the host system. To program the device, the user loads the 16 operating parameters, which define the transformation to be performed, which sections of the original and resampled image spaces are to be utilized, and various control words. Filtering operations are further defined by the values the user loads into the external coefficient memory. The transform parameters are described below. See also Tables 1 through 3.

| XMIN, XMAX,<br>YMIN, YMAX          | These four parameters outline the "source" rectangular region of the original image. Whenever the IRS pair generates an (X, Y) address within this boundary the CZERO flags will denote a valid memory read. In the most common case, XMIN < XMAX, YMIN < YMAX, 000h < X < FFFh, and 000h < Y < FFFh. In this case, addresses out of bounds cause one or both CZEROs to go LOW. Refer to Application Note TP-38 for further information on other boundary violation cases. Each parameter is expressed in 12-bit unsigned binary integer notation. See Figure 12.               |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UMIN,<br>UMAX,<br>VMIN, VMAX       | These four parameters outline the "target" region of the (u, v) plane, into which the resampled image will be written. The IRS will generate, line by line, a scan that fills only this portion of the plane, permitting the user to assemble a mosaic of multiple rectangular subimages. Care must be taken to ensure that UMAX > UMIN and VMAX > VMIN. Each parameter is expressed in 12-bit unsigned binary integer notation. See Figure 12.                                                                                                                                 |

| (X <sub>0</sub> , Y <sub>0</sub> ) | These are the coordinates of the first pixel to be read from the original image. In many applications, this point will be one of the four corners of the original image to be resampled. The pixels near (X <sub>0</sub> , Y <sub>0</sub> ) in the original image will be used to compute the upper left pixel of the transformed image. In non-inverting, non-reversing applications (X <sub>0</sub> , Y <sub>0</sub> ) will be the upper left corner of the original subimage. Each coordinate is expressed in 13-bit integer plus 5-bit fraction, two's complement notation. |

| dX/dU0             | Is the initial horizontal partial first derivative indicating the displacement along the X axis which corresponds to each one pixel movement along the U axis. Usually, 0 < dX/dU <sub>0</sub> < 1 corresponds to magnification, whereas dX/dU <sub>0</sub> > 1 represents reduction and dX/dU <sub>0</sub> < 0 denotes reflection about a vertical axis. The first derivatives are expressed in 8-bit integer, 12-bit fraction two's complement notation. |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dX/dV <sub>0</sub> | Is the initial horizontal-vertical partial first derivative. It indicates the displacement along the X axis corresponding to each one pixel movement along the V axis. The coefficients dX/dV <sub>0</sub> and dX/dU <sub>0</sub> define image rotation and shear.                                                                                                                                                                                         |

| dY/dU <sub>0</sub> | Is the initial vertical-horizontal partial first derivative. It indicates the displacement along the Y axis corresponding to each one pixel movement along the U axis.                                                                                                                                                                                                                                                                                     |

| dY/dV0             | Is the initial vertical partial first derivative. It indicates the displacement along the Y axis corresponding to each one-pixel step along the V axis. Since dX/dV0 and dY/dV0 are separate parameters, vertical magnification and reflection need not match their horizontal counterparts.                                                                                                                                                               |

#### Note:

1. For each incremental move along the U axis, the starting point of the new "walk around spiral" is indexed to the ENDING point of the previous walk around spiral, rather than to its center. Therefore, the terms dX/dU<sub>0</sub> and dY/dU<sub>0</sub> must be adjusted accordingly. Since each new line is referenced back to the previous line's initial spiral starting point, no similar dX/dV<sub>0</sub> or dY/dV<sub>0</sub> correction is needed.

| d <sup>2</sup> X/dU <sup>2</sup> | Is the second order horizontal derivative. It indicates the rate of change of the horizontal-horizontal first derivative with each step along a line in the output image space. All six second-order derivatives are 4-bit integer, 20-bit fractional two's complement parameters. |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d <sup>2</sup> X/dV <sup>2</sup> | Is the second order horizontal-<br>vertical-vertical derivative. It<br>indicates the rate of change of the<br>horizontal-vertical first derivative with<br>each step down a column in the<br>output image space.                                                                   |

| d <sup>2</sup> Y/dU <sup>2</sup> | Is the second order vertical-horizontal-horizontal derivative. It indicates the rate of change of the the vertical-horizontal first derivative with each step along a line of the output image space.                                                                                                       |                                              |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| d <sup>2</sup> Y/dV <sup>2</sup> | Is the second order vertical derivative. It indicates the rate of change of the vertical-vertical first derivative with each step down a column of the output image space.                                                                                                                                  |                                              |  |

| d <sup>2</sup> X/dUdV            | Is the mixed second order derivative indicating the rate of change of the first order horizontal derivative as one proceeds downwards through the output image space. This is also the rate of change of the first order horizontal-vertical derivative during horizontal sweeps in the output image space. |                                              |  |

| d <sup>2</sup> Y/dUdV            | Is the mixed second order derivative indicating the rate of change of the first order vertical derivative as one moves horizontally across the output space, or, equivalently, the rate of change of the first order vertical-horizontal derivative as one moves vertically in the output image space       |                                              |  |

| Row/Column<br>Select             | Sets the mode to either Row (0) or Column (1) operation.                                                                                                                                                                                                                                                    |                                              |  |

| Mode                             | This 2-bit control word defines three unique instructions:                                                                                                                                                                                                                                                  |                                              |  |

|                                  | Code                                                                                                                                                                                                                                                                                                        | Instruction                                  |  |

|                                  | 00, 01<br>10                                                                                                                                                                                                                                                                                                | single-pass operation pass 1 of two-pass     |  |

|                                  | 11                                                                                                                                                                                                                                                                                                          | operation<br>pass 2 of two pass<br>operation |  |

|                                  |                                                                                                                                                                                                                                                                                                             |                                              |  |

In single-pass operation, the device walks through the entire  $(k+1) \times (k+1)$  kernel for each output pixel, where k is the value written into the Kernel section (see below) of the parameter register. Two-pass operation, which requires a dimensionally separable kernel, is executed first for a (k+1) element kernel in one direction, then for a (k+1) element kernel in the other direction. For kernel sizes exceeding  $2 \times 2$ , the two-pass algorithm is obviously beneficial, requiring 2n samples per output point instead of  $n \times n$ . In this case, the intermediate image data stored in the destination image memory following the first pass is used as the source image data on the second pass. The user may design a system to

switch source and destination memory bank addresses in place, or could utilize a second TMC2301 pair in a pipelined architecture. This would require a third image buffer for the final destination image. Both devices of a system pair are usually set to the same mode.

| Kernel                    | The effective kernel width (height) exceeds this 4-bit unsigned number by 1, thereby providing kernels of 1 x 1 to 16 x 16 source pixels per output, for either resampling or filtering. Simple static filters can be implemented with kernels of up to 16 x 16 pixels (Kernel = 15), while resampling interpolation kernels are limited to 4 x 4 pixels (Kernel = 3), due to the four bits of fractional X (or Y) address generated by the TMC2301. See the Applications Discussion. Again, both devices in a pair are generally initialized with equal Kernel values. |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field of<br>View<br>(FOV) | As the device walks through its kernel coefficients, each corresponding step in (x, y) space is normally one pixel length or height; this is a field of view of 1. However, the user can subsample the original space before filtering or resampling, by applying the coefficient kernel over a view field of up to 7 units. At a field of view of F, the pixels selected for each kernel operation are F pixels apart. This is useful in oversampled pictures, whose intensity changes only slowly from pixel to pixel.                                                |

| Autoload<br>(ALR)         | When set to 1 (HIGH), the LDR control is automatically asserted when INIT is strobed, loading the coefficient set currently stored in the preload registers.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Autoinit<br>(AIN)         | At the end of an image, if the AIN bit is 1 (HIGH) the DONE flag goes HIGH for one clock cycle and a new transform begins. If 0 (LOW), UWRI and the DONE flag remain HIGH during the sequence until the user strobes the INIT control to begin a new image transformation.                                                                                                                                                                                                                                                                                              |

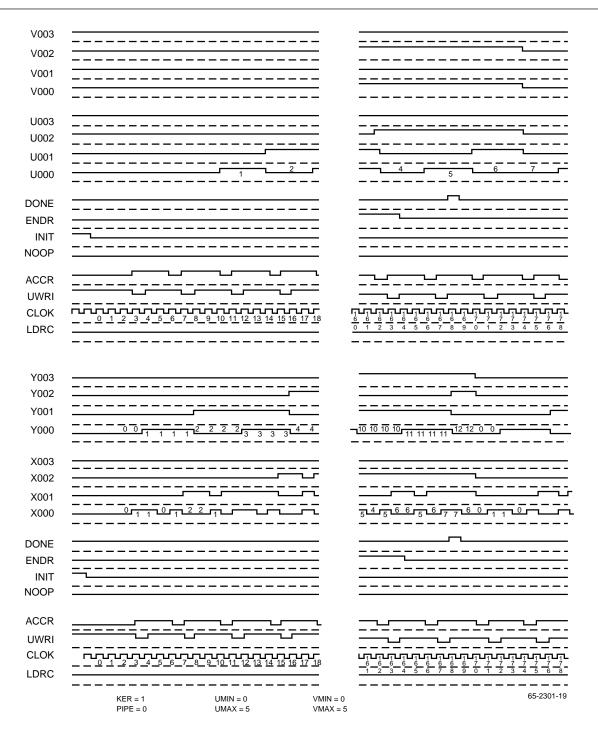

| Pipe<br>(PIPE)            | Adjusts the timing of the target memory write controls, to compensate for buffered source image RAM. If the PIPE bit is 1 (HIGH), outputs $\overline{ACC}$ and $\overline{UWRI}$ will be delayed one clock cycle relative to the generation of the target address (U or V). See Figure 9.                                                                                                                                                                                                                                                                               |

SIGN

12

4

11

INTERNAL ACCUMULATOR

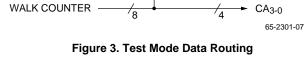

| Mode<br>(TM) | This mode is available for user inspection of the coefficient data. The source image and coefficient addresses are calculated by an internal 28-bit accumulator. When TM is 1 (HIGH), the sign bit, normally discarded, and the lower 11 bits of internal data are substituted for the upper 12 bits appearing at the source address port (X) during a standard transform cycle. This allows user verification of algorithm mathematics during debug. Since the TM bit is registered and cannot be changed during a single clock cycle, two distinct clock cycles are required to access both the MSW and LSW of the internal accumulator. See Figure 3. |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

T<sub>11</sub>

TEST MODE

X<sub>11-0</sub>/T<sub>11-0</sub>

CA7-4

Table 1. Parameter Registers – Row Sequencer

| Addr | Name                                   | Description                             |

|------|----------------------------------------|-----------------------------------------|

| 0000 | XMIN                                   | Left side of Source Window              |

| 0001 | XMAX                                   | Right side of Source Window             |

| 0010 | X <sub>0</sub> (LSW)                   | Source starting point –<br>X coordinate |

| 0011 | X <sub>0</sub> (MSW)                   | Source starting point –<br>X coordinate |

| 0011 | Controls                               | Mode Select Bits                        |

| 0100 | dX/dU <sub>0</sub> (LSW)               | Row/Row first differential              |

| 0101 | dX/dU <sub>0</sub> (MSW)               | Row/Row first differential              |

| 0101 | TM, FOV                                | Test Mode, Field of View                |

| 0110 | dX/dV <sub>0</sub> (LSW)               | Row/Column first differential           |

| 0111 | dX/dV <sub>0</sub> (MSW)               | Row/Column first differential           |

| 0111 | Kernel                                 | Resampling/Filtering Kernel             |

| 1000 | d <sup>2</sup> X/dUdV<br>(LSW)         | Mixed second differential               |

| 1001 | d <sup>2</sup> X/dUdV<br>(MSW)         | Mixed second differential               |

| 1010 | d <sup>2</sup> X/dU <sup>2</sup> (LSW) | Row second differential                 |

| 1011 | d <sup>2</sup> X/dU <sup>2</sup> (MSW) | Row second differential                 |

| 1100 | d <sup>2</sup> X/dV <sup>2</sup> (LSW) | Row/Column second differential          |

| 1101 | d <sup>2</sup> X/dV <sup>2</sup> (MSW) | Row/Column second differential          |

| 1110 | UMIN                                   | Left edge of Final Image                |

| 1111 | UMAX                                   | Right edge of Final Image               |

Table 2. Parameter Registers – Column Sequencer

| Addr | Name                                   | Description                             |

|------|----------------------------------------|-----------------------------------------|

| 0000 | YMIN                                   | Top of Source Window                    |

| 0001 | YMAX                                   | Bottom of Source Window                 |

| 0010 | Y <sub>0</sub> (LSW)                   | Source starting point –<br>Y coordinate |

| 0011 | Y <sub>0</sub> (MSW)                   | Source starting point –<br>Y coordinate |

| 0011 | Controls                               | Mode Select Bits                        |

| 0100 | dY/dU <sub>0</sub> (LSW)               | Column/Row first differential           |

| 0101 | dY/dU <sub>0</sub> (MSW)               | Column/Row first differential           |

| 0101 | TM, FOV                                | Test Mode, field of View                |

| 0110 | dY/dV <sub>0</sub> (LSW)               | Column/Column first differential        |

| 0111 | dY/dV <sub>0</sub> (MSW)               | Column/Column first differential        |

| 0111 | Kernel                                 | Resampling/Filtering Kernel<br>Sure     |

| 1000 | d <sup>2</sup> Y/dUdV (LSW)            | Mixed second differential               |

| 1001 | d <sup>2</sup> Y/dUdV (MSW)            | Mixed second differential               |

| 1010 | d <sup>2</sup> Y/dU <sup>2</sup> (LSW) | Column/Row second differential          |

| 1011 | d <sup>2</sup> Y/dU <sup>2</sup> (MSW) | Column/Row second differential          |

| 1100 | d <sup>2</sup> Y/dV2 (LSW)             | Column second differential              |

| 1101 | d <sup>2</sup> Y/dV <sup>2</sup> (MSW) | Column second differential              |

| 1110 | VMIN                                   | Top edge of Final Image                 |

| 1111 | VMAX                                   | Bottom edge of Final Image              |

Table 3. Parameter Registers Binary Format (Row or Column Sequencer)

|                    | Format          |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  | L                             | imits                |

|--------------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------------------------|----------------------|

| Address            | MSB             |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  | LSB              | Dec                           | Hex                  |

| 0000*              | 2 <sup>11</sup> | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 20               | 4095<br>0                     | FFF<br>000           |

| 0001*              | 2 <sup>11</sup> | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 4095<br>0                     | FFF<br>000           |

| 0010               | 2 <sup>6</sup>  | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 2 <sup>-1</sup>  | 2 <sup>-2</sup>  | 2 <sup>-3</sup>  | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 4096-2 <sup>-5</sup><br>-4096 | 0FFF.F8<br>F000.00   |

| 0011               |                 |                  |                  |                  |                  |                  | -2 <sup>12</sup> | 2 <sup>11</sup>  | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   |                               |                      |

| 0011<br>(Control)  | ALR             | AIN              | PIPE             | R/C              | M1               | M <sub>0</sub>   |                  |                  |                  |                  |                  |                  |                               |                      |

| 0100               | 2-1             | 2 <sup>-2</sup>  | 2 <sup>-3</sup>  | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 2 <sup>-6</sup>  | 2 <sup>-7</sup>  | 2 <sup>-8</sup>  | 2 <sup>-9</sup>  | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 128-2 <sup>-12</sup>          | 007F.FFF             |

| 0101               |                 |                  |                  |                  | -2 <sup>7</sup>  | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | -128                          | FF80.000             |

| 0101* (TM,<br>FOV) | TM              | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   |                  |                  |                  |                  |                  |                  |                  |                  |                               |                      |

| 0110               | 2-1             | 2 <sup>-2</sup>  | 2 <sup>-3</sup>  | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 2 <sup>-6</sup>  | 2 <sup>-7</sup>  | 2 <sup>-8</sup>  | 2 <sup>-9</sup>  | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 128-2 <sup>-12</sup><br>-128  | 007F.FFF<br>FF80.000 |

| 0111               |                 |                  |                  |                  | -2 <sup>7</sup>  | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 120                           | 1100.000             |

| 0111*<br>(Kernel)  | 2 <sup>3</sup>  | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   |                  |                  |                  |                  |                  |                  |                  |                  | 15<br>0                       | f<br>O               |

| 1000               | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> | 2 <sup>-18</sup> | 2 <sup>-19</sup> | 2 <sup>-10</sup> | 8-2 <sup>-20</sup><br>-8      | 0007.FFFFF           |

| 1001               | -2 <sup>3</sup> | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 2 <sup>-1</sup>  | 2-2              | 2 <sup>-3</sup>  | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 2 <sup>-6</sup>  | 2 <sup>-7</sup>  | 2 <sup>-8</sup>  | Ü                             |                      |

| 1010               | 2-9             | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> | 2 <sup>-18</sup> | 2 <sup>-19</sup> | 2 <sup>-10</sup> | 8-2 <sup>-20</sup><br>-8      | 0007.FFFFF           |

| 1011               | -2 <sup>3</sup> | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 2 <sup>-1</sup>  | 2-2              | 2-3              | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 2 <sup>-6</sup>  | 2 <sup>-7</sup>  | 2 <sup>-8</sup>  | Ü                             |                      |

| 1100               | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> | 2 <sup>-18</sup> | 2 <sup>-19</sup> | 2 <sup>-10</sup> | 8-2 <sup>-20</sup><br>-8      | 0007.FFFFF           |

| 1101               | -2 <sup>3</sup> | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 2 <sup>-1</sup>  | 2-2              | 2 <sup>-3</sup>  | 2 <sup>-4</sup>  | 2 <sup>-5</sup>  | 2 <sup>-6</sup>  | 2 <sup>-7</sup>  | 2-8              | -0                            |                      |

| 1110*              | 2 <sup>11</sup> | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 4095<br>0                     | FF<br>000            |

| 1111*              | 2 <sup>11</sup> | 2 <sup>10</sup>  | 2 <sup>9</sup>   | 2 <sup>8</sup>   | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup>   | 2 <sup>4</sup>   | 2 <sup>3</sup>   | 2 <sup>2</sup>   | 2 <sup>1</sup>   | 2 <sup>0</sup>   | 4095<br>0                     | FF<br>000            |

#### Notes:

1. \* unsigned binary notation

2. A "-" indicates MSB is sign bit

| <b>Internal Bit Mapping</b> (For parametric inputs, | integers in table are bits of P. the input point) |

|-----------------------------------------------------|---------------------------------------------------|

|-----------------------------------------------------|---------------------------------------------------|

|                                                                                                  | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | <b>2</b> <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2-2 | 2 <sup>-3</sup> | 2 <sup>-4</sup> |

|--------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|----------------|-----------------|-----|-----------------|-----------------|

| XOUT [11:0]                                                                                      |                 | 11              | 10              | 9              | 8              | 7              | 6              | 5              | 4              | 3                     | 2              | 1              | 0              |                 |     |                 |                 |

| C <sub>ADN</sub> [7:4]                                                                           |                 |                 |                 |                |                |                |                |                |                |                       |                |                |                | 7               | 6   | 5               | 4               |

| XMAX, XMIN                                                                                       |                 | 11              | 10              | 9              | 8              | 7              | 6              | 5              | 4              | 3                     | 2              | 1              | 0              |                 |     |                 |                 |

| Xo                                                                                               | 5               | 4               | 3               | 2              | 1              | 0              | 11             | 10             | 9              | 8                     | 7              | 6              | 5              | 4               | 3   | 2               | 1               |

| DX/DU, DX/DV                                                                                     |                 |                 |                 |                |                | 7              | 6              | 5              | 4              | 3                     | 2              | 1              | 0              | 11              | 10  | 9               | 8               |

| D <sup>2</sup> X/DUDV,<br>D <sup>2</sup> X/DU <sup>2</sup> ,<br>D <sup>2</sup> X/DV <sup>2</sup> |                 |                 |                 |                |                |                |                |                |                | 11                    | 10             | 9              | 8              | 7               | 6   | 5               | 4               |

|                                                                                                  | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> | 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> | 2 <sup>-18</sup> | 2 <sup>-19</sup> | 2 <sup>-20</sup> |

|--------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| XOUT [11:0]                                                                                      |                 |                 |                 |                 |                 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| C <sub>ADN</sub> [7:4]                                                                           |                 |                 |                 |                 |                 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| XMAX, XMIN                                                                                       |                 |                 |                 |                 |                 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| Xo                                                                                               | 0               |                 |                 |                 |                 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| DX/DU, DX/DV                                                                                     | 7               | 6               | 5               | 4               | 3               | 2                | 1                | 0                |                  |                  |                  |                  |                  |                  |                  |                  |

| D <sup>2</sup> X/DUDV,<br>D <sup>2</sup> X/DU <sup>2</sup> ,<br>D <sup>2</sup> X/DV <sup>2</sup> | 3               | 2               | 1               | 0               | 11              | 10               | 9                | 8                | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

## Operation of the Transformation Parameter Registers

Numerous applications require the ability to update the coordinate transformation parameters "on the fly." Because the parameters are double-buffered, the user can load any or all of them into the preload registers without upsetting the operation in progress. Then LDR (load data registers) will update all transform parameters to the new values simultaneously. This feature is particularly valuable for "pin cushion" and "fish eye" transformations, or polar-to-rectangular conversions which cannot be performed with constant second derivatives. The Autoload function updates the preread registers at the beginning of a new image automatically. See the Transformation Control Parameters section. Note also that data can be loaded in to the registers while  $\overline{\text{NOOP}}$  is active (LOW).

Figure 4. Operation of LDR Control for Parameter Update

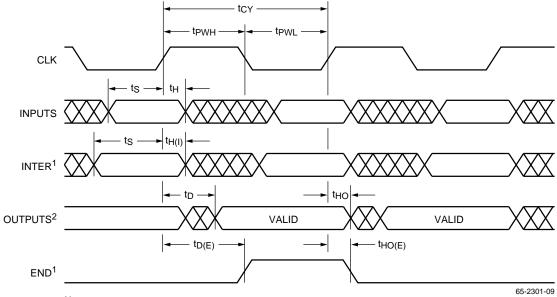

## **Timing Diagram**

#### Notes:

- 1. ts and tD(E) are guaranteed to allow full speed operation in the standard two-device architecture. See text.

- 2. All outputs except END. See text.

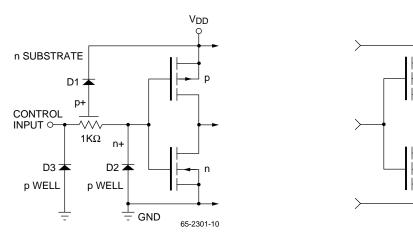

## **Equivalent Circuits and Transition Levels**

Figure 5. Equivalent Input Circuit

Figure 6. Equivalent Output Circuit

GND

$V_{\text{DD}}$

n SUBSTRATE

OUTPUT

► D1 p+

n+

■ D2

p WELL

65-2301-11

1. All outputs except CZERO, ACC, END and DONE.

Figure 7. Transition Level for Three-State Output

## Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min  | Тур | Max                   | Unit |

|----------------------------------------------------------------|------|-----|-----------------------|------|

| Supply Voltage                                                 | -0.5 |     | 7.0                   | V    |

| Input Voltage                                                  | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Output                                                         |      |     |                       |      |

| Applied Voltage <sup>2</sup>                                   | -0.5 |     | V <sub>DD</sub> + 0.5 | V    |

| Forced Current <sup>3,4</sup>                                  | -1.0 |     | 6.0                   | mA   |

| Short Circuit Duration (single output in HIGH state to ground) |      |     | 1                     | sec  |

| Temperature                                                    | ·    |     | · ·                   |      |

| Operating, Case                                                | -60  |     | 130                   | °C   |

| Operating, Junction                                            |      |     | 175                   | °C   |

| Lead Soldering (10 seconds)                                    |      |     | 300                   | °C   |

| Storage                                                        | -65  |     | 150                   | °C   |

#### Notes:

- 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

## **Operating Conditions**

|        |                                | ;    | Standar | Extende | d   |     |      |       |

|--------|--------------------------------|------|---------|---------|-----|-----|------|-------|

| Parame | ter                            | Min  | Тур     | Max     | Min | Тур | Max  | Units |

| VDD    | Supply Voltage                 | 4.75 | 5.0     | 5.25    | 4.5 | 5.0 | 5.5  | V     |

| VIL    | Input Voltage, Logic LOW       |      |         | 0.8     |     |     | 0.8  | V     |

| VIH    | Input Voltage, Logic HIGH      | 2.0  |         |         | 2.0 |     |      | V     |

| loL    | Output Current, Logic LOW      |      |         | 8.0     |     |     | 8.0  | mA    |

| ЮН     | Output Current, Logic HIGH     |      |         | -4.0    |     |     | -4.0 | mA    |

| TA     | Ambient Temperature, Still Air | 0    |         | 70      |     |     |      | °C    |

| TC     | Case Temperature               |      |         |         | -55 |     | 125  | °C    |

## **DC Characteristics** within specified operating conditions<sup>1</sup>

|       |                                              |                                                                                 | Te   | emperati | ure Ranç | ge   |       |

|-------|----------------------------------------------|---------------------------------------------------------------------------------|------|----------|----------|------|-------|

|       |                                              |                                                                                 | Stan | dard     | Exte     | nded |       |

| Param | eter                                         | Conditions                                                                      | Min  | Max      | Min      | Max  | Units |

| IDDQ  | Supply Current, Quiescent                    | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V                                     |      | 5        |          | 5    | mA    |

| IDDU  | Supply Current, Unloaded                     | V <sub>DD</sub> = Max, f = 15MHz                                                |      | 75       |          | 75   | mA    |

| IIL   | Input Current, Logic LOW                     | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V                                     | -10  | 10       | -75      | 75   | μА    |

| lін   | Input Current, Logic HIGH                    | VDD = Min, VIN = VDD                                                            | -10  | 10       | -75      | 75   | μΑ    |

| VoL   | Output Voltage, Logic LOW                    | V <sub>DD</sub> = Min, I <sub>OL</sub> = Max                                    |      | 0.4      |          | 0.4  | V     |

| Voн   | Output Voltage, Logic HIGH                   | VDD = Min, IOH = Max                                                            | 2.4  |          | 2.4      |      | V     |

| lozL  | Hi-Z Output Leakage<br>Current, Output LOW   | V <sub>DD</sub> = Min, V <sub>IN</sub> = 0V                                     | -40  | 40       | -40      | 40   | μА    |

| lozh  | Hi-Z Output Leakage<br>Current, Output HIGH  | V <sub>DD</sub> = Min, V <sub>IN</sub> = V <sub>DD</sub>                        | -40  | 40       | -40      | 40   | μА    |

| los   | Short-Circuit Output<br>Current <sup>2</sup> | V <sub>DD</sub> = Max, Output HIGH, one pin to ground, one second duration max. |      | -100     |          | -100 | mA    |

| Cı    | Input Capacitance                            | T <sub>A</sub> = 25°C, f = 1MHz                                                 |      | 10       |          | 10   | pF    |

| Co    | Output Capacitance                           | T <sub>A</sub> = 25°C, f = 1MHz                                                 |      | 10       |          | 10   | pF    |

#### Notes:

- 1. Actual test conditions may vary from those shown, but guarantee operation as specified.

- 2. Guaranteed but not tested.

## AC Characteristics within specified operating conditions

|        |                                |                                                 | Temperature Range |     |      |       |     |     |      |      |      |

|--------|--------------------------------|-------------------------------------------------|-------------------|-----|------|-------|-----|-----|------|------|------|

|        |                                |                                                 |                   |     | Star | ndard |     |     | Exte | nded |      |

|        |                                |                                                 |                   | ·2  | -    | ·1    |     |     |      |      |      |

| Parame | eter                           | Conditions                                      | Min               | Max | Min  | Max   | Min | Max | Min  | Max  | Unit |

| tcy    | Cycle Time                     | V <sub>DD</sub> = Min                           | 50                |     | 55   |       | 66  |     | 66   |      | ns   |

| tpwL   | Clock Pulse Width LOW          | V <sub>DD</sub> = Min                           | 20                |     | 22   |       | 25  |     | 30   |      | ns   |

| tpWH   | Clock Pulse Width<br>HIGH      | V <sub>DD</sub> = Min                           | 25                |     | 28   |       | 33  |     | 35   |      | ns   |

| ts     | Input Setup Time <sup>1</sup>  |                                                 | 15                |     | 18   |       | 20  |     | 20   |      | ns   |

| tH     | Input Hold Time                |                                                 | 1                 |     | 2    |       | 2   |     | 2    |      | ns   |

| tH(I)  | Input Hold Time, INTER         |                                                 | 8                 |     | 10   |       | 10  |     | 10   |      | ns   |

| tD     | Output Delay <sup>2</sup>      | VDD = Min, CLOAD = 40pF                         |                   | 25  |      | 27    |     | 35  |      | 35   | ns   |

| tD(E)  | Output Delay, END <sup>1</sup> | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 10pF |                   | 35  |      | 37    |     | 45  |      | 45   | ns   |

| tHO    | Output Hold Time <sup>2</sup>  | VDD = Max, CLOAD = 40pF                         | 5                 |     | 5    |       | 5   |     | 5    |      | ns   |

| tHO(E) | Output Hold Time, END          | V <sub>DD</sub> = Max, C <sub>LOAD</sub> = 10pF | 10                |     | 10   |       | 10  |     | 10   |      | ns   |

| tDIS   | Three-State Disable<br>Delay   | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40pF |                   | 25  |      | 27    |     | 35  |      | 35   | ns   |

| tENA   | Three-State Enable<br>Delay    | VDD = Min, CLOAD = 40pF                         | 25                |     | 27   |       | 35  |     | 35   |      | ns   |

- 1. ts + tD(E) = tcy max.

- 2. Excluding output pin END.

## **Applications Discussion**

#### **Basic Operation**

Each TMC2301 pair contains address controllers which execute patterns much like the following FORTRAN 3-level nested DO loop:

- 1. The inner loop is a clockwise outgoing spiral "walk" through the N-element coefficient kernel.

- 2. The middle loop is a left-to-right "scan" along each row of the output image space.

- 3. Finally, the outer loop is a top-to-bottom "scan" down each column of the output image space.

A typical one pass image transformation proceeds as follows:

1. The device pair outputs the addresses  $(X_0, Y_0)$ , which is the first point in the source image, and (CAX, CAY), the interpolation lookup table address for the first pixel in the kernel. The output  $\overline{ACC}$  goes LOW, causing the

- external accumulator to load the first product without summation, clearing the accumulator.

- 2. For the next N cycles, the IRS walks through an outward clockwise spiral in (x, y) space, accumulating pixel-interpolation coefficient products. The spiral sequence is depicted in Figure 8.

- 3. After the completion of the first spiral walk, the IRS outputs the target address of the first pixel, (UMIN, VMIN) and the control UWRI, along with the initial (X, Y) values of the next spiral walk. ACC and UWRI can be delayed by one clock cycle by setting the control bit PIPE to 1 (HIGH) simplifying the task of interfacing the TMC2301 to buffered source image memory.

- After the last cycle of the next spiral, <u>UWRI</u> again goes LOW for one clock, and the target address outputs are updated, pointing to the location of the pixel calculation just completed, (UMIN + 1, VMIN).

- 5. The third spiral walk begins with  $\overline{ACC}$  going LOW, and ends with (UMIN + 2, VMIN) output and UWRI going LOW.

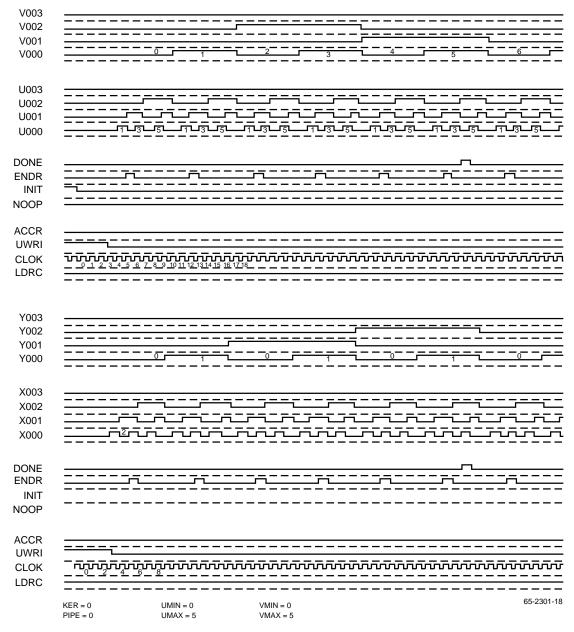

Figure 8. Timing Diagram and Pixel Map Showing Outward Clockwise Spiral Walk Generated by TMC2301 (2x2 Kernel Shown)

6. The procedure continues until (UMAX + 1, VMIN) is reached, at which point the device resets to U (position within row) and increments V (number of row). Thus, the next (U, V) set after (UMAX + 1, VMIN) will be (UMIN, VMIN + 1), followed by (UMIN + 1, VMIN + 1), etc.

7. Upon completion of the walk corresponding to (UMAX + 1, VMAX + 1), the TMC2301 will generate a DONE flag with the final \overline{UWRI}, and begin a new sequence.

On any given clock cycle, the actual (X, Y) and (U, V) outputs of the IRS are given by the following equations:

$$\begin{split} x &= X_0 + dX/dU_0 * m + dX/dV_0 * n + d^2X/dUdV * m * n \\ &+ d^2X/dU^2 * (m2 - m)/2 + d^2X/dV^2 * (n^2 - n)/2 \\ &+ FOV * CAX(w) + FOV * m * CAX(Ker) \end{split}$$

$$\begin{split} y &= Y_0 + dY/dU_0 * m + dX/dV_0 * n + d^2Y/dUdV * m * n \\ &+ d^2Y/dU^2 * (m2 - m)/2 + d^2Y/dV^2 * (n^2 - n)/2 \\ &+ FOV * CAY(w) + FOV * m * CAY(Ker) \end{split}$$

u = UMIN + m

v = VMIN + n

where FOV is the 4-bit field of view parameter, normally set to 1 so that the spiral walk proceeds in single-pixel steps. Setting FOV to 4 would expand the spiral walk, allowing the user to trade two bits of image size for two bits of additional interpixel positioning resolution. CAX(w) and CAY(w) are the current value of the coefficient address outputs and CAX(KER) and CAY(KER) are the terminal values of each pixel walk. The CA(KER) terms arise because the IRS computes each new walk's starting paint from the previous spiral walk's end point rather than its starting point.

## Interpolation Coefficient Lookup Table Addressing

The external coefficient lookup table RAM stores the interpolation values used to calculate the value of the new pixel. These values are selected by the user allowing maximum filtering flexibility. In simple filtering applications, all 8 bits of coefficient address are available to access up to 256 interpolation coefficients, for kernels of 16 x 16 pixels. This address is generated by the internal walk counter of the TMC2301. In most applications, the same Kernel parameter value is selected in both IRS devices; thus, the Coefficient Address outputs CA7-0 for the X and Y devices are identical, and the user needs only one of the 8-bit buses for memory access.

Applications executing a coordinate transformation, however will almost always generate non-integer source pixel addresses; that is the U (or V) locations will not map to the X (or Y) addresses exactly and fractional address components

are generated. The user then must account for this spatial offset in both dimensions by storing the appropriate corrected interpolation kernel values in the lookup table. The 8-bit address bus is broken up into two parts: the fractional portion (upper 4 bits), and the walk counter (lower 4 bits). Thus, in resampling applications, the maximum kernel size is 4 x 4 pixels, or 16 locations. As in the filtering example, assuming that the user has selected the same kernel size for both IRS devices, the 4 bits of least-significant address generated by both devices will be identical and redundant. The four most significant address bits, however, will reflect the current fractional offsets of the resampled pixel from the nearest X (Y) location, to a spatial resolution of 4 bits in the X (or Y) directions. Utilization of the 12 bits (total) of lookup table address is left to the user to be arranged as desired for memory access. See Figure 3.

#### **Application Examples**

One of the more common applications for the TMC2301 is simple static filtering In this case the source and target memories locations are identical and no coordinate transformation is performed. The (X,Y) and (U,V) outputs listed in Table 4 show the address sequencing generated by the TMC2301 to execute the walk of a 5 x 5 pixel interpolation kernel. The normalized coefficients shown implement a first-order Butterworth Low Pass Filter with cutoff radius of  $1/\sqrt{2}$ . Note that the (U,V) output address is updated following the completion of the walk for that location.

Figure 9. Pixel Map Showing Walk Sequence for 5x5 Static Filter

Table 4. IRS Outputs for Static Filter Illustrated in Figure 10

|       |   |     | Index |             |   |   |

|-------|---|-----|-------|-------------|---|---|

| Cycle | X | Υ   | (CA)  | Coefficient | U | V |

| 1     | 3 | 4   | 0     | 0.2176      | 2 | 4 |

| 2     | 4 | 4   | 1     | 0.0725      | 2 | 4 |

| 2 3   | 4 | 5   | 2     | 0.0435      | 2 | 4 |

| 4     | 3 | 5   | 3     | 0.0725      | 2 | 4 |

| 5     | 2 | 5   | 4     | 0.0435      | 2 | 4 |

| 6     | 2 | 4   | 5     | 0.0725      | 2 | 4 |

| 7     | 2 | 3   | 6     | 0.0435      | 2 | 4 |

| 3     | 3 | 3   | 7     | 0.0725      | 2 | 4 |

| 9     | 4 |     | 8     | 0.0435      | 2 | 4 |

| 10    | 5 | 3   | 9     | 0.0198      | 2 | 4 |

| 11    | 5 | 4   | 10    | 0.0272      | 2 | 4 |

| 12    | 5 | 5   | 11    | 0.0198      | 2 | 4 |